Die Signalabtastung erfolgt Timer gesteuert in festen Zeitintervallen. Bei einer µC Taktfrequenz von 16MHz und 1µs (1MHz) Abtastrate stehen zur Auswertung eines Samples nur 16 µC Zyklen zur Verfügung. Eine Implementierung ohne Interrupts ist hier von Vorteil, da das Speichern & Laden des Statusregisters ebenso entfällt wie die RETI Instruktion, die alleine 4 µC Zyklen beansprucht. Für brauchbare Ergebnisse der Zeit- und Frequenzmessung sollte die Abtastung mit wenigstens der 5-fachen Frequenz des Eingangssignals erfolgen. Nachfolgendes Bild zeigt die Messung eines symmetrischen 500kHz Signals, das trotz der Abtastung mit nur 1µs (1MHz) einen gleichförmigen Verlauf aufweist.

Da für die schnelleren Signalabtastungen nur wenige µC Taktzyklen zur Verfügung stehen, erfolgt die Prüfung der Triggerbedingung erst im PC Programm durch Analyse des Speicherinhalts. Nach dem Start einer Messung werden zunächst 2000 Samples mit den gewählten Intervallen im SRAM des µC gespeichert. Erst danach wird der SRAM Inhalt per RS232 an den PC übertragen. Dort wird das Speicherabbild nach dem erstmaligen Auftreten der Triggerbedingung durchsucht.

Die Hardware ist denkbar einfach: Der ATmega328 wird mit einem 16MHz Quarz getaktet, womit nur noch Port D 8 Signaleingänge für die Messungen bereitstellt; diese sind mit externen Pull down Widerständen versehen; daher müssen ungenutzte Signaleingänge in der Triggermaske mit 0 spezifiziert werden. Zudem stehen PD0 & PD1 nicht als USART Interface (RxD, TxD) zur Verfügung. Die RS232 Übertragung erfolgt hier gemäß Atmel Application Note 305 per Bit Bang über die frei wählbaren Pins PC0 & PC1. 2 LED dienen zur Statusanzeige: Grüne LED => Messung läuft, rote LED => RS232 Übertragung des µC Puffers zum PC. Auch das Delphi Benutzerinterface weist einen entsprechenden Indikator auf. Es wurde mit Delphi3 erstellt, benötigt keine Installation und kommt ohne zusätzliche Komponenten aus.

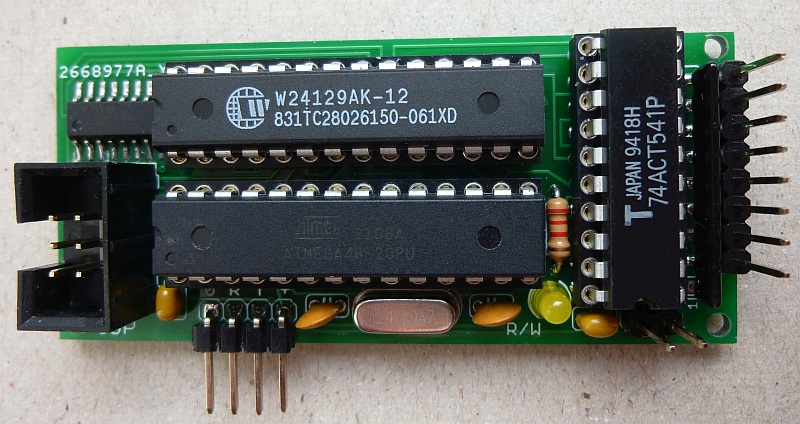

In einem nächsten Schritt habe ich die in (1) beschriebene Architektur mit externem RAM und externem Adresszähler zwar beibehalten, diese jedoch so abgeändert, dass der µC während der Messung nur noch den Takt für den Adresszähler erzeugt. Das Einlesen der Signale erfolgt nun weitgehend ohne Zutun des µC per Hardware. Statt des D-FlipFlops an den Eingängen in (1) wird ein Buspuffer verwendet, der nur zu Beginn der Messung aufgeschaltet wird, und der nicht bei jeder Abtastung getaktet werden muss. Hiermit sind immerhin Abtastraten von bis zu 12MHz möglich - dem 12-fachen Wert des obigen Designs! Zur Aufnahme der Messwerte dient hier ein 16kByte RAM. Die Grundversion nutzt nur die ersten 4kByte, die der 12 Bit Adresszähler direkt ansteuert. Die beiden zusätzlichen Adressbits können aber vom µC gesteuert werden.

Das PC Benutzerinterface nutzt das gleiche Verfahren wie oben, es müssen nur einige Konstanten geändert werden. Meinen 2-lagigen Platinenentwurf hierzu habe ich diesmal extern fertigen lassen. Näheres auf Anfrage.